#### **ROADMAP • OPEN ACCESS**

# 2022 roadmap on neuromorphic devices and applications research in China

To cite this article: Qing Wan et al 2022 Neuromorph. Comput. Eng. 2 042501

View the article online for updates and enhancements.

# You may also like

- Hadamard product-based in-memory computing design for floating point neural network training

Anjunyi Fan, Yihan Fu, Yaoyu Tao et al.

General spiking neural network framework for the learning trajectory from a noisy mmWave radar

Xin Liu, Mingyu Yan, Lei Deng et al.

- <u>Designing polar textures with ultrafast</u> neuromorphic features from atomistic <u>simulations</u>

Sergey Prosandeev, Sergei Prokhorenko, Yousra Nahas et al.

# **NEUROMORPHIC**

Computing and Engineering

#### **OPEN ACCESS**

RECEIVED 15 November 2021

REVISED

17 June 2022

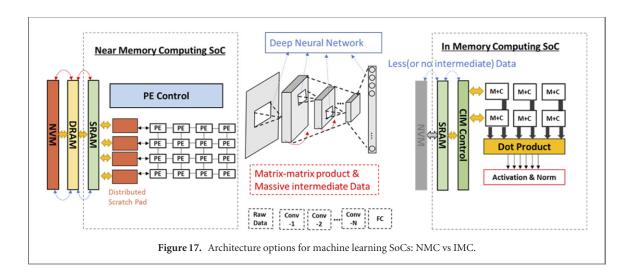

ACCEPTED FOR PUBLICATION 20 June 2022

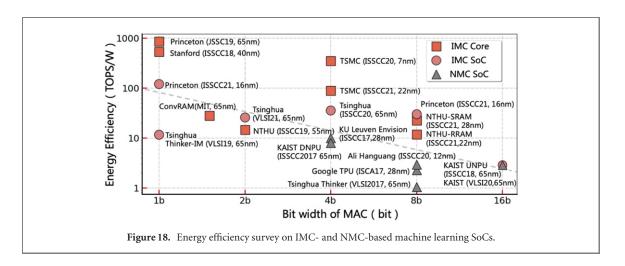

PUBLISHED

8 December 2022

Original content from this work may be used under the terms of the Creative Commons Attribution 4.0 licence.

Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

#### **ROADMAP**

# 2022 roadmap on neuromorphic devices and applications research in China

Qing Wan<sup>1,23,\*</sup>, Changjin Wan<sup>1,23,\*</sup>, Huaqiang Wu<sup>2,23</sup>, Yuchao Yang<sup>3,23</sup>, Xiaohe Huang<sup>4</sup>, Peng Zhou<sup>4</sup>, Lin Chen<sup>4</sup>, Tian-Yu Wang<sup>4</sup>, Yi Li<sup>5,6</sup>, Kan-Hao Xue<sup>5,6</sup>, Yu-Hui He<sup>5,6</sup>, Xiang-Shui Miao<sup>5,6</sup>, Xi Li<sup>7</sup>, Chenchen Xie<sup>7</sup>, Houpeng Chen<sup>7</sup>, Zhitang Song<sup>7</sup>, Hong Wang<sup>8</sup>, Yue Hao<sup>8</sup>, Junyao Zhang<sup>9</sup>, Jia Huang<sup>9</sup>, Zheng Yu Ren<sup>10,11,12</sup>, Li Qiang Zhu<sup>10,11</sup>, Jianyu Du<sup>13</sup>, Chen Ge<sup>13</sup>, Yang Liu<sup>14</sup>, Guanglong Ding<sup>15</sup>, Ye Zhou<sup>15</sup>, Su-Ting Han<sup>14</sup>, Guosheng Wang<sup>16</sup>, Xiao Yu<sup>16</sup>, Bing Chen<sup>17</sup>, Zhufei Chu<sup>18</sup>, Lunyao Wang<sup>18</sup>, Yinshui Xia<sup>18</sup>, Chen Mu<sup>4</sup>, Feng Lin<sup>4</sup>, Chixiao Chen<sup>4</sup>, Bojun Cheng<sup>19</sup>, Yannan Xing<sup>20</sup>, Weitao Zeng<sup>20</sup>, Hong Chen<sup>2</sup>, Lei Yu<sup>21</sup>, Giacomo Indiveri<sup>19,22</sup> and Ning Qiao<sup>19,20,22</sup>

- School of Electronic Science and Engineering, Nanjing University, Nanjing, People's Republic of China

- <sup>2</sup> Tsinghua University, Beijing, People's Republic of China

- <sup>3</sup> Peking University, Beijing, People's Republic of China

- State Key Laboratory of ASIC and System, School of Microelectronics, Fudan University, Shanghai 200433, People's Republic of China

- School of Integrated Circuits, School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, People's Republic of China

- Hubei Yangtze Memory Laboratories, Wuhan 430205, People's Republic of China

- Shanghai Key Laboratory of Nanofabrication Technology for Memory, Shanghai Institute of Micro-System and Information Technology, Chinese Academy of Sciences, People's Republic of China

- 8 Key Laboratory of Wide Band Gap Semiconductor Technology, School of Microelectronics, Xidian University, Xi'an 710071, People's Republic of China

- <sup>9</sup> Interdisciplinary Materials Research Center, School of Materials Science and Engineering, Frontiers Science Center for Intelligent Autonomous Systems, Tongji University, Shanghai, 201804, People's Republic of China

- School of Physical Science and Technology, Ningbo University, Ningbo 315211, Zhejiang, People's Republic of China

- Ningbo Institute of Materials Technology and Engineering, Chinese Academy of Sciences, Ningbo 315201, Zhejiang, People's Republic of China

- 12 School of Physical Science and Technology, ShanghaiTech University, Shanghai 201210, People's Republic of China

- Beijing National Laboratory for Condensed Matter Physics, Institute of Physics, Chinese Academy of Sciences, Beijing 100190, People's Republic of China

- Institute of Microscale Optoelectronics, Shenzhen University, Shenzhen 518060, People's Republic of China

- $^{\rm 15}$   $\,$  Institute for Advanced Study, Shenzhen University, Shenzhen 518060, People's Republic of China

- Research Center for Intelligent Chips, Zhejiang Lab, Hangzhou 311121, People's Republic of China

- $^{\rm 17}~$  School of Micro-Nano Electronics, Zhejiang University, Hangzhou 310058, People's Republic of China

- <sup>18</sup> Faculty of Electrical Engineering and Computer Science (EECS), Ningbo University, Ningbo, People's Republic of China

- 19 SynSense AG, Thurgauerstrasse 40, 8050 Zurich, Switzerland

- <sup>20</sup> Chengdu SynSense Tech. Co. Ltd., 1577 Tianfu Road, Chengdu, Sichuan, People's Republic of China

- School of Electronic and Information, Wuhan University, 299 Bayi Road, Wuhan, People's Republic of China

- <sup>22</sup> University of Zurich, Rämistrasse 71, 8006, Zurich, Switzerland

- \* Authors to whom any correspondence should be addressed.

- <sup>23</sup> Guest editors of the roadmap.

$\hbox{$E$-mail: wanqing@nju.edu.cn and $cjwan@nju.edu.cn}$

Keywords: neuromorphic computing, memristors, in-memory computing, 2D memristors, neuromorphic devices, China

# Abstract

The data throughput in the von Neumann architecture-based computing system is limited by its separated processing and memory structure, and the mismatching speed between the two units. As a result, it is quite difficult to improve the energy efficiency in conventional computing system, especially for dealing with unstructured data. Meanwhile, artificial intelligence and robotics nowadays still behave poorly in autonomy, creativity, and sociality, which has been considered as the unimaginable computational requirement for sensorimotor skills. These two plights have urged the imitation and replication of the biological systems in terms of computing, sensing, and even motoring. Hence, the so-called neuromorphic system has drawn worldwide attention in recent decade, which is aimed at addressing the aforementioned needs from the mimicking of neural

system. The recent developments on emerging memory devices, nanotechnologies, and materials science have provided an unprecedented opportunity for this aim.

This roadmap profiles the potential trend in building neuromorphic systems from the view of Chinese scientists. The content of this roadmap will cover some core topics from multidisciplinary researchers, including electronics, computer science, materials, physics, and so on. The perspectives and challenges are also discussed partly, which may serve as guidance for the pursuing of high energy-efficient and/or bio-realistic systems that can compute, sense, and act as our human beings. This will also give birth to some excited paradigm breakers and advanced technologies in a wide spectrum of areas.

#### **Contents**

| Int | roduction                                                                        | 2  |

|-----|----------------------------------------------------------------------------------|----|

| 1.  | From memristors to neuromorphic computing                                        | 4  |

| 2.  | Two-dimensional two-terminal memristors                                          | 7  |

| 3.  |                                                                                  |    |

| 4.  | Neuromorphic devices and applications based on phase-change random-access memory |    |

| 5.  | Physically transient memristors for neuromorphic computing                       | 14 |

| 6.  |                                                                                  |    |

|     | to system                                                                        | 16 |

| 7.  | Brief discussion of oxide neuromorphic transistors in China                      | 20 |

| 8.  |                                                                                  |    |

| 9.  | Development of 2D-based neuromorphic transistor in China                         | 26 |

|     | Neuromorphic transistor for bionic perception                                    |    |

| 11. | . Neuromorphic computing going efficient                                         | 31 |

| 12. | . Automated synthesis and mapping                                                | 34 |

| 13. | . Survey on machine learning SoC: from near-memory computing to IMC              | 37 |

| 14. | Market-oriented neuromorphic SoC solution                                        | 40 |

| Acl | knowledgments                                                                    | 41 |

| Da  | ta availability statement                                                        | 42 |

|     | forences                                                                         | 12 |

#### Introduction

Changjin Wan and Qing Wan

Nanjing University, People's Republic of China

E-mail: cjwan@nju.edu.cn and wanqing@nju.edu.cn

The recent surge in artificial intelligence (AI) drives the exploration of machine learning hardware, especially the development of fundamental building blocks, namely, neuromorphic devices. China is becoming one of the most thriving regions of this research field. The general aim of the *roadmap on neuromorphic devices* and applications research in China is to provide an overview of the different fields of research and progress that are related to neuromorphic devices and applications, evaluate the possible technical routes and challenges, and give guidelines and perspectives that would shed light on future development. The roadmap addresses the following topics:

- Materials for neuromorphic devices

- Applications and tools for neuromorphic devices and systems

- Perspectives for neuromorphic computing

Materials for neuromorphic devices. The development of neuromorphic devices is still dependent on what materials can render. Even the scaling of state-of-the-art (SOTA) complementary metal-oxide-semiconductor (CMOS) technologies benefits from the utilizing of advanced materials. For example, the success of fin-shaped field-effect transistor (FinFET) was partly attributed to the implementation of high- $\kappa$  dielectric materials. In view of transistor-type neuromorphic devices, proper semiconducting materials would bring about low off current, which could improve the energy efficiency; high mobility, which is important for increasing switch speed of the devices; and high sensitivity/selectivity to certain stimulations, which might benefit near- or in-sensor computing. Dielectric materials for memristor-type neuromorphic devices should also be subject

to significant attention, as the mechanisms of a memristive neuromorphic device, including redox, phase change, magnetic tunneling, and ferroelectric polarization, are mostly determined by the dielectric materials. Therefore, we collected several sections under this topic, and we promise that with the exploring of emerging materials and refining of the conventional materials, these will offer new opportunities for the development of neuromorphic electronics.

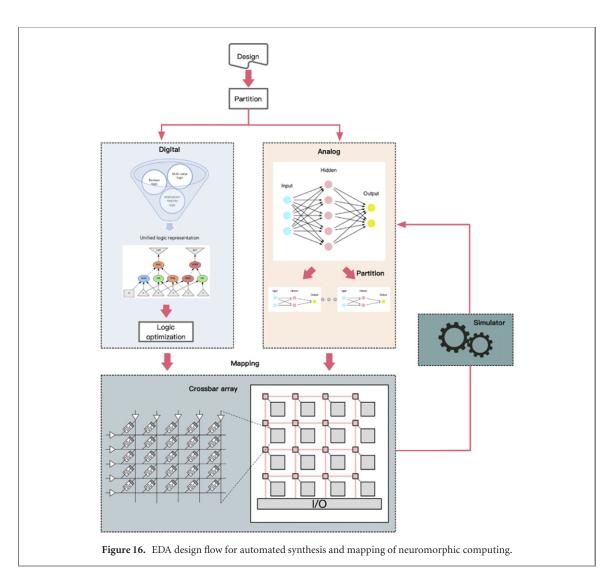

Applications and tools for neuromorphic devices and systems. Another important research field with respect to neuromorphic devices is to make them practicable. Emerging applications based on neuromorphic devices that could advance the conventional digital system in certain aspects, like energy efficiency, error tolerance, plasticity, and so on, will be highly pursued. For example, the realization of artificial perception based on neuromorphic devices has potential implications for future robotics that might have humanlike sophisticated sensorimotor capabilities within a very narrow energy budget. Besides, to boost efficiency from design to manufacturing, it is very necessary to develop electronic design automation (EDA) tools, and it would be possible to extend the application and generality of neuromorphic computing and engineering by developing automated synthesis and mapping techniques.

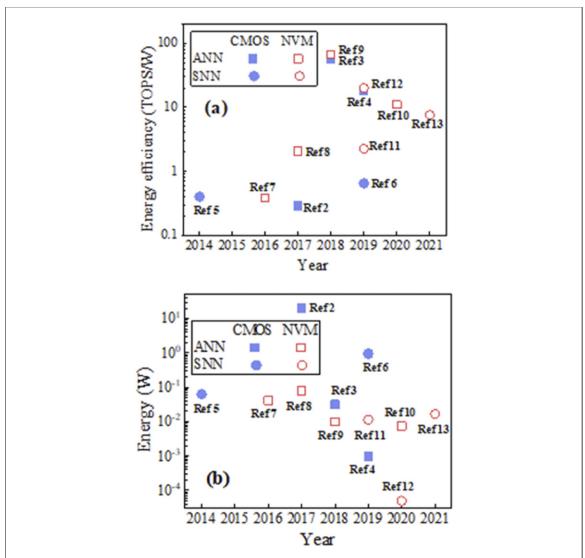

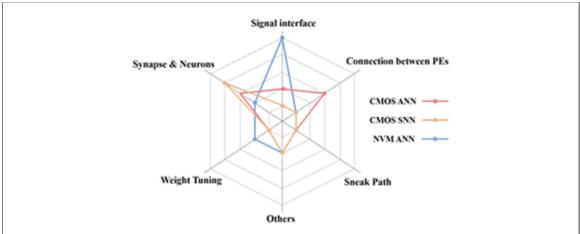

Perspectives for neuromorphic computing. The ultimate aim of neuromorphic devices is to build a neuromorphic system that operates similarly to our neural networks (NNs). A short-term goal would be focused on the implementation of nonvolatile memory (NVM) technique for improving the energy efficiency of machine learning algorithms. The NVM array has shown excellent energy efficiency in dealing with matrix—matrix multiplication, which is a computing- and memory-intensive workload and is not efficient in conventional CPU-like von Neumann architectures. In this trend, system-on-chip (SoCs) accelerating NN computing is widely reported for different specific applications, such as image recognition, keyword spotting, and natural language processing. However, several tough challenges should be addressed before taking full advantage of the neuromorphic device-based SoCs. Development in this trend will also bring with it unprecedented opportunities that could come from many aspects, like algorithm—circuit—architecture codesign, introduction of event-driven process, novel NN structures, and so on.

# 1. From memristors to neuromorphic computing

Xiaohe Huang and Peng Zhou\* Fudan University, People's Republic of China E-mail: pengzhou@fudan.edu.cn

#### 1.1. Status

Resistive memory originates from the reversible resistive effect induced by electrical pulses reported in the 1960s [1]. In 1971 Chua proposed a theoretical model of a memristor, predicting its resistive state would change with the history of applied voltage [2]. By 2008 experimentally demonstrated TiO<sub>2</sub>-based resistive random-access-memory (RRAM) devices first linked RRAM with memristors [3]. With a simple 'sandwich' structure, memristors have been developed to a very small size with low power consumption, and they can perform the function of storing and even processing information excellently [4]. When it is unknown whether memristors can shake the position of mature flash memory as the mainstream NVM, it is expected to serve as the most desirable basic device unit for implementing synaptic and neuronal functions in the emergence of neuromorphic computing. The data transfer and speed gap between conventional computing and memory make the data processing waste a huge amount of energy and time. The so-called memory wall problem generated by the von Neumann bottleneck becomes more and more urgent. Neuromorphic computing, which mimics the nervous system in the biological brain, uses analog signals to process information with high parallelism, low power consumption, and convergence of storage and computing [5]. So neuromorphic computing has a natural advantage over digital systems in solving computational tasks faster and more efficiently in a smaller

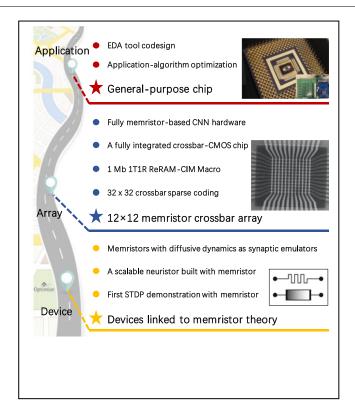

Since the first memristor device simulation to implement synaptic functions in 2010 [6], memristor-based neuromorphic devices are now able to mimic the basic functions of biological neurons and synapses. Among them, memristors have been the most studied as simple artificial synapses, whereby integrated arrays can directly rely on physics laws to perform efficient parallel in-memory computations [7], such as accelerating vector-matrix multiplication in artificial neural network (ANN) training and inference. Classical machine learning tasks, such as information encoding [8], data classification [9], and reinforcement learning [10], can already be implemented in them. Neuromorphic computing is more efficient than the current traditional computing paradigm in the demanded environment of internet of thing (IoT), which requires available ultralow-power intelligent edge computing. Memristors are the most promising underlying devices since artificial neurons that simulate biological functions based on physical principles enable a simpler and more efficient circuitry than CMOS [11]. Although further development of artificial neural devices is a great challenge, it is a promising way to implement complex human brain systems in hardware (figure 1).

### 1.2. Current and future challenges

Although neuromorphic devices have made some progress from the device level to the array level, they are still a long way from real application, and many technical bottlenecks remain to be solved [12]. Device yields and uniformity for memristors are still not sufficient. The microscopic process of resistive material change is inherently stochastic [13]. The random movement of ions or thermal activation of defects may lead to fluctuation of device parameters, thus reducing uniformity and yield. Even though the yield and uniformity of NVM for binary values can be easily achieved, memristors for multilevel states face higher requirements [14]. Nonlinearity and asymmetry constrain the application of the devices, and the limited number of tunable weight states limits the computing accuracy [15]. Other metrics to evaluate memristors as neuromorphic devices include retention, endurance, and on/off ratio. Devices that meet the requirements in all performance metrics are still lacking to facilitate the design of general-purpose systems. How to design and select materials and mechanisms for neuromorphic devices to manufacture high-precision devices is still a central issue for researchers to consider.

At the array level, the sneak-path currents generated by the applied voltage on unselected devices hinder the read/write operation of the memristors, limiting the large-scale integration of crossbar arrays [16]. On the other hand, if the size scales down and the array scales up, the wire resistance inside the arrays will inevitably increase, which leads to a voltage drop on the wire, significantly affecting the signal transmission, and limits the accuracy of the calculation while also increasing power consumption [17]. At the system application level, algorithms with their practical applications that fully manifest the advantages of neuromorphic computing are important factors to drive the industry forward. Most of the current research is modifying device properties to better fit on available algorithms, which limits the inherent properties of materials and devices, so algorithms that are more closely tied to the device are needed. For example, there is a lack of proven algorithms especially for spiking neural networks (SNNs) [5].

Figure 1. Roadmap for the development of memristor-based neuromorphic computing. Memristors have made milestones on the road to neuromorphic computing, from devices to arrays, but demonstrations of their systems and applications are still in the initial stages. Applicable systems and algorithms are necessary for the future realization of the goal of general-purpose neuromorphic computing in the long term. Panel inset 'devices linked to memristor theory' is reproduced from reference [3]. Panel inset '12  $\times$  12 memristor crossbar array' is reproduced from reference [7]. Panel inset 'fully memristor-based CNN hardware' is reproduced from reference [11].

#### 1.3. Advances in science and technology to meet challenges

The development and maturation of a new computing paradigm will inevitably confront many obstacles. With the combined efforts and wisdom of the research community and the advancement of science and technology, it is feasible to overcome the challenges encountered at all levels from device to array to the system. For the underlying device stability, the uniformity of the device can be improved by limiting the position of the conductive filament (CF) (for example, by introducing dislocation defects [18] and localized doping [19]) or by increasing the device  $R_{\rm off}/R_{\rm on}$  ratio (by reducing device area [20] to increase  $R_{\rm off}$  for the filamentary type) to compensate for resistance fluctuation. The nonlinear weights can also be alleviated with optimized programming methods [15] using programming pulses that are adapted to the device characteristics for operation. The problem of asymmetry can be overcome by combining multiple devices as a unit structure [21]. Just as silicon is to CMOS technology, finding the materials and structures that best fit the function of the memristors may be the fundamental solution to these device problems.

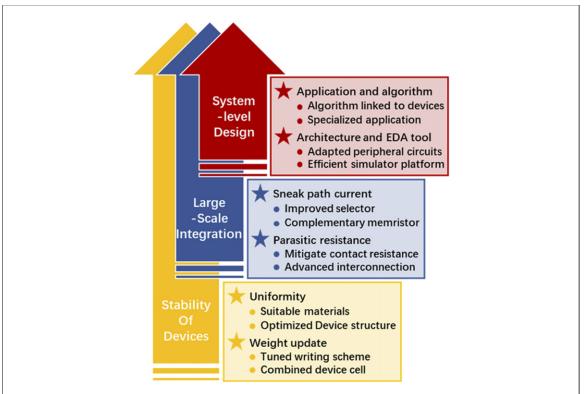

To allow the array size to be scaled up, it is possible to minimize the sneak-path current by using better selectors [22], and another attempt is to build complementary memristors [23]. An ideal selector is as critical as the memristor in determining the ceiling of the array size. Parasitic resistance between interconnects is also a major challenge affecting array performance. Finding a better conductive material for the wire or using more advanced interconnects to reduce parasitic resistance is a goal that researchers have been working on. A further compromise to mitigate the need for large arrays is combining multiple small arrays to implement different layers of computing. The design of the top-level system influences the collaboration between each level from top to bottom. The algorithms developed according to the properties of the underlying devices can mitigate the stringent requirements for the devices and arrays [17]. A successful algorithm can also lead to customized, specialized applications, unlocking the potential of brain-inspired computing. A generic, proven architecture is the bedrock for building a system, where the design of peripheral circuitry incurs a substantial overhead. Compatible high-performance conversion circuits and controllers enable more efficient data flow within the system. What can be learned from the mature CMOS technology is that EDA tools can effectively collaborate on the design of the entire system at a hierarchical level. Creating an efficient simulation platform will facilitate integrated development from the bottom to the top (figure 2).

**Figure 2.** Challenges and possible solutions for memristor-based neuromorphic computing. The hierarchical architecture from the top application algorithm to the underlying device is intrinsically linked and needs to be optimized in collaboration with each other.

#### 1.4. Concluding remarks

The traditional computing paradigm has become unsustainable under the demands of today's big data and IoTs. Neuromorphic computing with memristors is a shock to the ecosystem that has long been dominated by silicon-based CMOS technology and von Neumann architecture. Although neuromorphic computing has the theoretical potential to be very disruptive, the progress made so far has not yet demonstrated its advantages for immediate application. The challenges it faces are not intangible; to overcome them requires joint research efforts across disciplines. It is expected that breakthroughs in materials science or even at the physical mechanism level will greatly improve the performance of neuromorphic devices. Theoretical advances in neuroscience are also contributing to a better understanding of biological computational behavior, which could potentially inspire more efficient algorithms. The mutual development of software, hardware, and theory will lay the foundation for the realization of ultimate brain-inspired intelligence.

# Acknowledgements

This work was supported by the National Natural Science Foundation of China (61925402, 61851402, 62004040, and 62090032), Science and Technology Commission of Shanghai Municipality (19JC1416600), Shanghai Education Development Foundation, and Shanghai Municipal Education Commission Shuguang Program (18SG01).

# 2. Two-dimensional two-terminal memristors

Lin Chen\* and Tian-Yu Wang Fudan University, People's Republic of China

E-mail: linchen@fudan.edu.cn and tywang@fudan.edu.cn

#### 2.1. Status

The application of AI technology has promoted the progress of the information age and put forward higher requirements for computing functions for the electronic devices. Traditional computers with von Neumann architecture are facing bottlenecks, such as bandwidth mismatch and huge energy consumption, inspiring the development of novel computing paradigm with in-memory computing (IMC) capability and low power consumption. Emerging devices and materials are needed for the development of novel computing architecture. Neuromorphic computing memristors are promising physical devices to construct IMC system, which show advantages of scalability, high density integration, high-speed operation, and low power consumption [24–26].

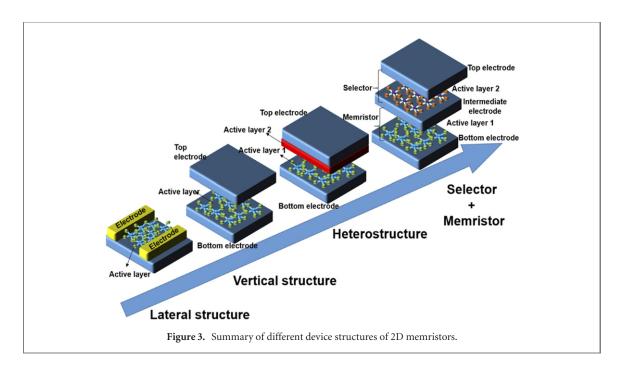

As the feature size of integrated circuits (ICs) gradually moves toward physical limits, it is hard to follow Moore's law under the feature size below 1 nm for traditional silicon-based semiconductor devices. Twodimensional (2D) layered materials as a promising candidate could work with a thickness of sub-1 nm, showing great potential in next-generation semiconductor materials due to high mobility, capability of overcoming short channel effects, and great size reduction, such as graphene, hexagonal boron nitride (h-BN), molybdenum disulfide (MoS<sub>2</sub>), tungsten disulfide, and indium selenide [27–33]. Efforts have been made to prepare 2D memristors for neuromorphic computing applications. Various device structures have been proposed to improve the performance of 2D memristors, including lateral structure, vertical structure, heterostructure, and 'one-selector one-memristor' (1S1M) structure [4, 34–36] (figure 3). The lateral structure-based memristor consists of two horizontal electrodes, and it is beneficial to introducing ions or other materials for modification research. The vertical structure-based memristor consists of a top electrode, a bottom electrode, and a middle active layer, which is the mainstream device structure. There is one more functional layer in heterostructurebased memristors than the vertical structure. For the circuit-level application of neuromorphic computing, the 1S1M structure that combines a selector and a memristor was proposed. Vacancy defect accumulation and CF migration are the main mechanisms in most reported 2D memristors. The 2D memristors may provide more possibilities for a new era of IMC.

# 2.2. Current and future challenges

Over the past 10 years the 2D memristors have been studied to act as the core components of neuromorphic computing system. However, the CMOS process compatibility, integration capability, reliability, stability, and unclear mechanisms of 2D neuromorphic computing memristors still limit their industrialization and promotion [37]. The reports of 2D memristors are focused on the demonstration of a single device, and the challenge is mainly in the growth of wafer-scale 2D materials for memristor array. Although 2D films could be prepared by chemical vapor deposition, the high temperature is not CMOS compatibility, which limited the promotion of this process. Due to the high temperature and long process time, it is hard to obtain a large-area 2D film for heterogeneous integration with silicon-based ICs. Second, the challenge for 2D neuromorphic computing memristors is reliability and stability. Due to the random defect density in different samples, the electrical properties of 2D memristors are hard to control. More studies focused on the optimization of crystallinity by developing the thin-film growth process to obtain uniform device performances. Third, the sneak-path current of crossbar array limited the integration capability of 2D neuromorphic computing devices. Although 2D materials could easily scale down to sub-nanometer level and integrated to 3D structure, the sneak-path current problem should be solved by integrating different 2D functional units. For future 2D neuromorphic computing electronics, the unclear mechanisms of devices and biological NN need to be investigated for better simulating biological behaviors by 2D memristors and achieving high-efficiency computing.

#### 2.3. Advances in science and technology to meet challenges

From the perspective of material growth, it is in urgent need to develop a suitable process compatible with CMOS technology to fabricate 2D memristors. Atomic layer deposition and advanced transfer technology provide more possibility for fabrication of large-area 2D memristors. From the perspective of device design, further optimization of device structure and lattice defects with the help of advanced electron beam lithography process and rapid thermal annealing process would be helpful to improve performance of device. From the perspective of array integration, the development of a two-terminal selector, a three-terminal transistor, and self-rectifying device would be helpful to solve the problem of leakage and sneak-path current in neuromorphic computing crossbar array based on 2D memristors [38, 39]. From the perspective of mechanism,

advanced characterization methods in biological and IC disciplines, such as *in situ* electron beam microscope and conductive atomic force microscopy, would be helpful to understand the work mechanism.

# 2.4. Concluding remarks

The 2D memristors have shown great potential in low power consumption, small size, and bandgap adjustable and flexible neuromorphic computing electronics. Although the CMOS process compatibility, integration capability, reliability, stability, and work mechanisms of 2D memristors are still challenges, the advanced fabrication process, transfer technology, characterization methods, and novel device structure could help to break the development bottlenecks and push the promising 2D memristor-based neuromorphic computing system.

#### Acknowledgements

L Chen and T Wang contributed equally to this work. This work was supported by the National Key Research and Development Program of China (2021YFA1202600), National Natural Science Foundation of China (92064009, 61904033, and 62004044), Program of Shanghai Subject Chief Scientist (18XD1402800), National Postdoctoral Program for Innovative Talents (BX2021070), Zhejiang Lab's International Talent Fund for Young Professionals, China Postdoctoral Science Foundation (2021M700026), the Young Scientist Project of the Ministry of Education Innovation Platform, and Support Plans for the Youth Top-Notch Talents of China.

#### 3. Metal-oxide memristors for IMC

Yi Li<sup>1,2</sup>, Kan-Hao Xue<sup>1,2</sup>, Yu-Hui He<sup>1,2</sup> and Xiang-Shui Miao<sup>1,2</sup>

- <sup>1</sup> Huazhong University of Science and Technology, People's Republic of China

- <sup>2</sup> Hubei Yangtze Memory Laboratories, People's Republic of China

Email: liyi@hust.edu.cn, xkh@hust.edu.cn, heyuhui@hust.edu.cn and miaoxs@hust.edu.cn

#### 3.1. Status

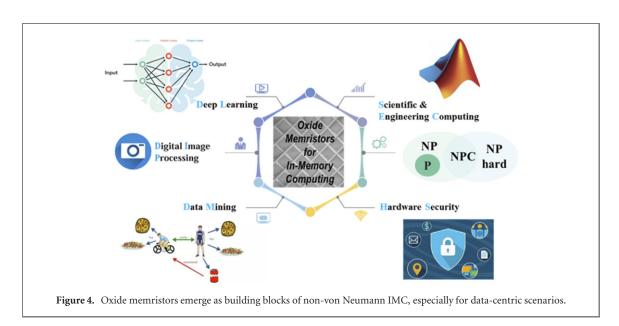

The memristor concept was theorized in 1971 by Professor Chua, and in 2008 researchers at HP Labs linked the concept to the experimentally studied oxide resistive devices [40, 41]. Owing to the advantages of high speed (down to 100 ps), low power consumption (down to femtojoule), high endurance ( $>10^{12}$ ), high scalability (down to 2 nm size), three-dimensional (3D) stacking capability ( $4F^2/n$ ; n is the number of 3D stacked layers), and the back end of line (BEOL) process compatibility, not only can the memristors meet the requirements of high-performance NVM applications (in this case, RRAMs), but they also show the ability to perform basic computation operators, such as Boolean logic and dot product operations. The idea of memristors as a cornerstone of memory and IMC in the post-Moore era has gained widespread acceptance (figure 4) [4, 11, 42].

Dating back to the 1960s, Hickmott reported the low-frequency negative resistance phenomenon in metal oxide devices, and after decades of exploration a large group of oxides with metal/insulator/metal device configurations have been reported to show frequency-dependent pinched hysteresis loops, typical fingerprints predicted by Chua [40, 41]. Compared with complex oxides, like  $SrTiO_3$ ,  $BiFeO_3$ , and  $Pr_{0.7}Ca_{0.3}MnO_3$ , simple binary amorphous metal oxides (especially  $HfO_x$ ,  $TaO_x$ ,  $WO_x$ , and  $AlO_x$ ) are in the spotlight of academia and industry because of their SOTA performance and low process cost. A number of oxide-based memristor array prototypes (up to Mb-class capacity) have already been developed (table 1).

In addition to the next-generation universal memory receiving the most attention, the binary switching behavior of memristors has been proposed to perform stateful logic to complement conventional charge-based logic, and high reconfigurability has been achieved with these memristors. Generic memristor arithmetic logic unit and some application-specific hardware for logic-intensive computing scenarios (data query, Hamming distance calculation, exclusive-OR [XOR] encryption, etc) have been demonstrated to provide efficient alternatives.

Besides, in recent years, the multilevel or analog properties of memristors have been fully exploited to emulate the weight updating and storage behaviors of biological synapses, and thus applied to the development of highly intriguing brain-inspired neuromorphic devices and systems. In addition, based on the analog matrix computing capability of crossbar arrays, accelerators for various machine learning algorithms (such as clustering, classification, regression, deep networks, and combinational optimization) have been developed with astounding improvements in computing power and energy efficiency (>100 tera-operations per second [TOPS] W<sup>-1</sup>) over conventional processors, like CPU and graphic processing unit (GPU).

#### 3.2. Current and future challenges

To outstand from various device candidates for IMC, memristors must overcome challenges, including elucidating the physical origin, device optimization, large-scale integration, and industrial applications.

Although it has been intensively exploited by first-principle calculation, *in situ* characterization, and device modeling [43, 44], an in-depth understanding of resistive switching behaviors in the vast range of memristor materials is still to be achieved. For a typical binary oxide HfO<sub>x</sub> that works under the binary switching mode, the CF has recently been revealed to be crystalline metal phases [44], whose formation and rupture account for the large resistive window. However, for doped oxides and the memristive materials designed for gradual resistance modulation, the exact physical origin, such as metal filaments, interfacial switching, or defective leakage paths, still needs to be clarified for various materials and/or doping schemes, which is also the basis for further optimization of device performance. Such understanding is particularly critical for analog computing applications, where a stable, high-precision programming is highly desirable and meanwhile nonlinearity, variability, and other nonideal factors should be effectively suppressed.

At the array level, the successfully demonstrated one-transistor one-resistor macros are limited by the large transistor area [45–48]. One-selector (Ovonic threshold switches, insulator-metal transition switches, or metallic filament-based threshold switches) one-resistor architecture is a viable compact alternative yet far from mature [49, 50]. Here the biggest challenge is to improve the overall performance, including drive capability, selectivity, endurance, and uniformity. In favor of low leakage and large switching window, the metallic CF-type oxide selectors are superior to Ovonic or metal-insulator transition types. Nonetheless, the advantages of CF selectors are offset by the random nature of ion migration, slow relaxation process, and atomic

**IOP** Publishing **2** (2022) 042501 Roadmap

Table 1. Summary of SOTA oxide memristor arrays.

| Туре                                 | Passive<br>array                    | 1T1R arra                                               | ny <sup>23 23</sup> 1T1R       | : 1 transistor and 1 resistor | 4T2R                            | 1S1R                                                                                                            | array                  | Self-rectifying array                                                                                                                           | Special<br>3D<br>stacking       |

|--------------------------------------|-------------------------------------|---------------------------------------------------------|--------------------------------|-------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Year                                 | 2019 [11]                           | 2020 [45]                                               | 2021 [46]                      | 2021 [47]                     | 2020 [48]                       | 2013 [49]                                                                                                       | 2021 [50]              | 2021 [51]                                                                                                                                       | 2020 [25]                       |

| Device                               | Au/<br>WO <sub>x</sub> /<br>Au      | TiN/<br>TaO <sub>x</sub> /<br>HfO <sub>x</sub> /<br>TiN | W/<br>TiN/<br>TiO <sub>2</sub> | ${\rm O_x}$ ReRAM             | Ta/<br>TaO <sub>x</sub> /<br>Pt | W/AlO <sub>x</sub> /<br>TaO <sub>y</sub> /<br>Ta <sub>2</sub> O <sub>5-x</sub> /<br>Pt/TiN/<br>AsTeGeSiN<br>TiN |                        | t Hf <sub>0.8</sub> Si <sub>0.2</sub> O <sub>2</sub> /<br>Al <sub>2</sub> O <sub>3</sub> /Hf <sub>0.5</sub> Si <sub>0.5</sub><br>O <sub>2</sub> | Ti/<br>Hf0 <sub>2</sub> /<br>Ta |

| Device size ( $\mu$ m <sup>2</sup> ) | 0.25                                | 0.25                                                    | 0.025                          | 0.022                         | 0.16-0.29                       | 0.5                                                                                                             | 100                    | 900                                                                                                                                             | 0.6                             |

| Transistor node (nm)                 | ) NA                                | 180                                                     | 22                             | 14, FinFET                    | 16                              | NA                                                                                                              | NA                     | NA                                                                                                                                              | NA                              |

| Array size                           | 5 kb                                | 2 kb                                                    | 4 Mb                           | 1 Mb                          | $\sim$ 1 kb                     | 64 bit                                                                                                          | 1 kb                   | 100 kb                                                                                                                                          | 4 kb                            |

| Application                          | Analog IMO<br>(machine<br>learning) | U                                                       | Binary<br>IMC<br>(CNN)         | Memory                        | Binary<br>IMC<br>(TCAM)         | Memory                                                                                                          | Analog<br>IMC<br>(SNN) | Analog IMC<br>(matrix<br>multiplication)                                                                                                        | Binary<br>IMC<br>(CNN)          |

accumulation that leads to the drawbacks of large variation, long latency, and limited lifetime. Other nonlinear devices, like self-rectifying memristors, are candidates with 3D integration potential [25, 51, 52]. However, a dense oxide tunneling or barrier layer introduced to provide reverse rectification usually leads to a significant increase in the operating voltage (exceeding 5 V or even 10 V), and thus unfavorable power consumption.

At the application level, a new functionality proposes new demands on device performance [42]. First, in situ learning requires frequent updating of device conductance, implying that endurance improvement needs to be focused on. Breakthroughs in computing energy efficiency also mean that the power consumption (both write and read) must be consistently reduced. Second, quantization and variation-aware algorithms to compensate for the limited accuracy and non-idealities also have to be developed. In addition, efficient programming methods in arrays, peripheral circuits to support parallel computing, and analog-to-digital and digital-to-analog conversion modules remain technical challenges. Besides, how to realize high-precision computing using low-precision memristors appears to be a substantial challenge with great scientific value [53].

#### 3.3. Advances in science and technology to meet challenges

To address the challenges mentioned previously, a collaborative strategy of hardware and software is required, with the pull of specific applications. For the NN accelerators or neuromorphic computing systems, recent developments with vacancy-deficient/vacancy-rich structures (such as  $TaO_{2-x}/Ta_2O_{5-x}$  and  $Al_2O_3/AlO_x$ ) are particularly promising since high performance and reliability have been demonstrated while the materials and

processes are compatible with CMOS [49]. The asymmetric structure can create a vacancy profile to control CF formation, which in turn precisely modulates the device conductivity. Besides, this multilayer structure helps to enhance the overall resistance, and hence reduces the read power consumption. In this way, the energy efficiency of the inference process may be significantly improved. For hardware/software collaboration, write-with-verify or closed-loop methods are widely employed to realize high precision (6–7 bits) programming. Other designs, such as quantization or binary NNs, have also been proposed to mitigate the harsh requirements of device analog properties. Efficient training algorithms, along with improvement in device endurance, together offer the possibility of *in situ* training implementation.

In contrast to the IMC with compelling analog devices, binary IMC does not require high-precision programming and has the potential for commercialization in the short to medium term using the currently available device technology, and therefore deserves better attention from researchers. For instance, binary memristor-based ternary content-addressable memories (TCAMs) have been experimentally demonstrated for pattern matching, showing superior performance over the traditional static random-access-memory (SRAM)-based TCAMs [48, 54]. Particular attention has been paid to strategies of leveraging digital IMC to speed up hyperdimensional computing, one-shot learning, and database query, which involve a large number of comparison and logic operations on binary sequences, with significantly higher energy efficiency over CMOS processors [54, 55]. Besides, the use of the bit slicing concept in binary crossbar, redundancy programming strategy, and mixed-precision architecture has been proved to be efficient approaches to improve the precision of IMC [42, 53, 56].

#### 3.4. Concluding remarks

In summary, the promising incorporation of high-performance memory and computing capabilities allows metal-oxide memristors to become one of the building blocks for beyond-Moore non-von Neumann computing architecture. The International Roadmap for Devices and Systems and the Institute of Electrical and Electronics Engineers Rebooting Computing Committee believe that at the crossroads where Moore's law is difficult to sustain, the IMC paradigm is the way to go, with the collaborative development of new technologies from the device, circuit, architecture, and algorithm levels. To promote the commercial application of memristors, efforts must be paid to mechanism characterization, device design and optimization, BEOL integration, and killer applications research. Interdisciplinary and cross-level innovation is needed to understand and overcome the challenges. Although IMC is still in its fancy and needs further extensive investigation in the next 5–10 years, especially on the generality and energy efficiency limits of this technology, the maturity of oxide memristor technology will lay a solid device foundation for high-performance computing (HPC) systems. We also believe that in the ubiquitous cloud and edge computing, memristor-based IMC will play a pivotal role.

#### Acknowledgements

The authors gratefully acknowledge support from the National Key R&D Program of China (Grant No. 2019YFB2205100), National Natural Science Foundation of China (Grant No. 61874164 and 92064012), Hubei Key Laboratory of Advanced Memories, Hubei Engineering Research Center on Microelectronics, and Chua Memristor Institute.

# 4. Neuromorphic devices and applications based on phase-change random-access memory

Li Xi, Xie Chenchen, Chen Houpeng and Song Zhitang Chinese Academy of Sciences, People's Republic of China

E-mail: ituluck@mail.sim.ac.cn, xcc@mail.sim.ac.cn, chp6468@mail.sim.ac.cn and ztsong@mail.sim.ac.cn

#### 4.1. Status

The advent of big data and AI era has brought unprecedented challenges to the conventional hardware platforms based on von Neumann architecture, such as 'storage wall' and 'power wall'. To address these issues, a novel conception of neuromorphic computation was first proposed by Mead in 1990 [57]. It has attracted extensive attention with high parallelism, low power consumption, and integration of storage and computation. In the past decade, great progress has been made in constructing neuro-inspired computing systems by imitating the information processing mechanism of biological brain nervous system through mainstream CMOS technology, including Neurogrid [58], TrueNorth [59], Loihi [60], and Tianjic [61]. However, the Moore's law constraint, complex peripheral circuits, volatility, and incapability of online learning hinder the development of more advanced transistor-based neuro-inspired systems.

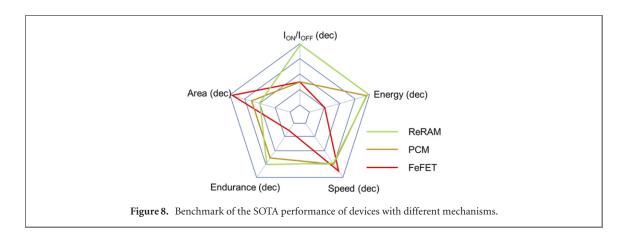

On the other hand, depending on unique mechanism, more and more novel structure devices start to directly mimic the behavior of synapses and neurons from the physical level, so as to construct the neuromorphic computing systems. Thus, these devices are also called neuromorphic devices. Most neuromorphic devices are expanded from emerging NVMs with their superior speed and power consumption than flash and excellent analog conductance regulation, like RRAM [46], ferroelectric random-access memory (FeRAM) [62], and magnetic random-access memory (MRAM) [63]. Phase-change random-access memory (PCRAM), as a competitive candidate, utilizes the large resistance contrast between amorphous and crystalline states of chalcogenide materials to store information and shows tremendous potentials in the field of neuromorphic computations [64]. The research of IBM shows that by optimizing the material composition and device structure of PCRAM, more than 1000 resistance states of memory cell can be realized [65], which lays a foundation for realizing multi-precision analog computation. Taiwan Semiconductor Manufacturing Company (TSMC) compared the image recognition performance of convolutional neural networks (CNNs) based on PCRAM, RRAM, and MRAM, respectively, and the result proved that PCRAM can achieve higher inference accuracy due to its larger resistance ratio [66]. In 2020, Peking University and Shanghai Institute of Microsystem and Information Technology realized the local high-precision training of CNNs [67], eligibility traces for energy-efficient reinforcement learning [68], and uncertainty quantification applications [69] with the multiresistance-level of PCRAM chip. In 2021, a 14 nm CMOS and phase-change-memory (PCM)-based IMC core with 10.5 TOPS W<sup>-1</sup> energy efficiency and 1.59 TOPS mm<sup>-2</sup> performance density is presented by IBM. Therefore, the application of PCRAM as a neuromorphic device is the most promising approach to break through the bottleneck of energy efficiency, integration, memorability, and online learning in the field of neuro-inspired computing systems.

#### 4.2. Current and future challenges

Despite the privileged advantages of PCRAM as a neuromorphic device to construct the neuro-inspired computing system due to the increasing process of materials science and the technology accumulated in mass production, there are still some inevitable obstacles impeding its further development in higher-level intelligent applications. First, higher reliability, lower power consumption, and window value of conductance are the most fundamental requirements of PCRAM as kernel device in a high-performance and energy-sensitive neuromorphic computing hardware. The reliability is embodied in the program/read speed, thermal stability, retention, and endurance, which are directly related to the performance of hardware and also urgent issues to be solved as novel memory. The power consumption of PCRAM mainly originates from the programming pulses driven by instantaneous current, which acts as the update of synaptic weight in neuro-inspired computation. The window value of device conductance is associated with the bit width of synaptic weight and will eventually affect the accuracy of computation. Second, the key point when imitating the behavior of NNs is to mimic the synaptic plasticity that refers to a characteristic or phenomenon of adjustable connection strength between neurons. Whether long-term synaptic plasticity (LTSP), short-term synaptic plasticity, or spike-timing-dependent plasticity (STDP), all these kinds of synaptic plasticity are embodied as electricinduced controllable conductance in neuromorphic device. However, owing to the fast phase transition and unique asymmetric switching mechanism of PCRAM, limited linearity and symmetry of conductance regulation can be achieved currently. In addition, since the biological neural system is generally composed of billions of neurons connected by trillions of synapses, in the application of PCRAM devices imitating NNs on a large-scale, the device variability has to be a hard nut to crack in mass production. Last but not least, as a

unique phenomenon of PCRAM device, resistance drift, mainly caused by structural relaxation [70], is also an ineluctable challenge in practical application scenarios.

# 4.3. Advances in science and technology to meet challenges

To address the mentioned challenges, it is essential to form cross-level collaborative innovation and optimization strategies, including materials, devices, manufacturing process, circuits, and algorithms. Research on materials science, like optimizing composition and doping engineering, cannot only reduce the melting point of PCRAM device to cut down the energy consumption [71], but it also retards the crystallization to obtain the linear and progressive conductance regulation [72]. Furthermore, high-thermal-stability doping can enhance the reliability so as to avoid the excessive complexity of hardware training and the loss of computing accuracy. Employing new materials, like carbon nanotubes or graphene as electrode and advanced device shield, can obviously improve the heating efficiency during write program and restrict inter-device variability, respectively. In terms of device design and structure, the specific thin conducting surfactant layers [73, 74] and the phase-change heterostructure [75] have been proved to be further effective in restricting resistance drift. As for circuit and array design, differential mTnR cell structure and reference cell-based resistance tracking provide a set of feasible solution for symmetrical conductance regulation and device uniformity. Finally, associated with the algorithms, PCRAM-based neuromorphic computing hardware platforms with high accuracy and energy efficiency will lead to a promising future in practical applications.

#### 4.4. Concluding remarks

Neuro-inspired computing is a systematic research involving multiple disciplines, and various emerging memory devices have been tested recently for their suitability. The PCRAM technology, as the most mature and promising neuromorphic device, is expected to become the core technology to replace existing von Neumann architecture and realize the in-memory-computing, which can achieve great breakthrough in computing and energy efficiency.

# Acknowledgements

This work was supported by the National Natural Science Foundation of China (91964204 and 92164302), Strategic Priority Research Program of Chinese Academy of Sciences (XDB44010200), and Science and Technology Council of Shanghai (19JC1416801), and in part by the Shanghai Research and Innovation Functional Program (17DZ2260900).

# 5. Physically transient memristors for neuromorphic computing

Hong Wang\* and Yue Hao Xidian University, People's Republic of China

E-mail: hongwang@xidian.edu.cn

#### 5.1. Status

Physically transient electronics is a new class of technology that the devices and/or systems are designed to physically disappear after completing the specific functions [76]. This concept is proposed by John Rogers in 2012, and electronic devices based on materials that can dissolve in water or bio-fluids have been reported. Physically transient devices based on biodegradable materials demonstrate excellent potential for hardware security, bio-integrated electronics, and implantable medical system applications [77, 78]. On the other hand, brain-inspired neuromorphic computing systems using the co-location of logic and memory concepts, offering a promising solution for the lower power consumption and highly efficient computing that can break through the limits of the von Neumann bottleneck [4]. Combining the advantages of physically transient electronics and neuromorphic computing to develop physically transient neuromorphic computing systems would have a unique advantage and excellent potential for brain–machine communication, such as prosthetics, *in situ* biosignal recording and feedback, and implantable and/or bio-integrated neural medicine like adaptive biohybrid interfaces, and repair communication between neurons and security computing system applications.

Various emerging devices, such as PCM, FeRAM, and RRAM, have been proposed to perform as artificial neuromorphic devices [79]. Among these, memristor is a promising candidate due to its simple structure, flexible material selection, low power, and high efficiency in computing. So physically transient memristor-based neuromorphic computing has great advantages in brain–computer interface, security electronics, and bio-integrated systems. Physically transient devices, including transistor, diode, and sensors, using biocompatible and biodegradable materials were firstly demonstrated in 2012 [76]. The physically transient memristor based on natural biopolymer with dissolvable properties was proposed in 2016 [80]. Transient memristor to mimic biological synaptic functions had already been demonstrated in 2018 [81]. Thereafter, material optimization and device design of memristor for physically transient neuromorphic devices have demonstrated their feasibility to simulate biological synapses and neurons [82–84]. Materials, including Mg, W, and Mo for electrodes and MgO, ZnO, and MoO<sub>x</sub> for switching layers, have shown great advantages for transient memristor application. Although the electrical performance of physically transient memristors still cannot compare with conventional memristors based on transition metal oxides, and integrated arrays are still lacking, the development of physically transient memristors is at a very early stage and faces great challenges, but it has a promising future for physically transient neuromorphic systems.

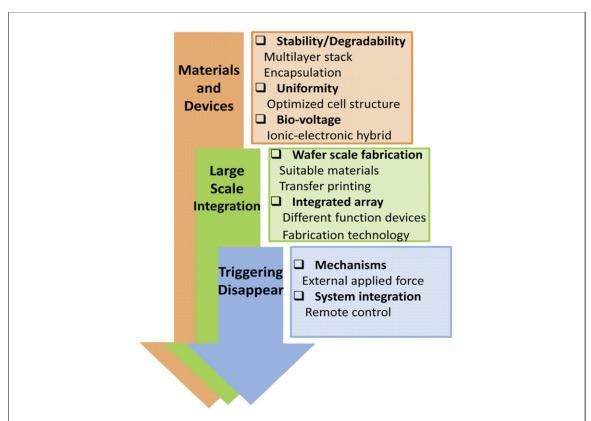

#### 5.2. Current and future challenges

Physically transient memristors have made rapid progress from materials to the larger-area array fabrication technology, but there remain several fundamental and technical challenges to be resolved. Stability and degradability of transient memristors always show a competitive relationship. However, they should meet the requirements of maintaining stable electrical characteristics with negligible variation with time and physically disappearing immediately after completing their functions or encountering a trigger signal. The currently available transient memristors are mostly based on biodegradable and dissolvable materials, which suffer from degradation in ambient environment. The mechanism and methods to balance the stability and degradability are still a challenge. The device performance of transient memristors, especially endurance and device-to-device uniformity characteristics, is far behind the demand of neuromorphic computing. How to design materials and device constructions to meet the requirements for long-term stability and quick degradability as well as the remarkable electrical performance for neuromorphic device application are basic and central issues.

For integrated array, compatibility with a larger area and with the high-density nano-fabrication technology is the key to commercialization and is still a challenge. On the other hand, feasibility of device size scaling down needs to be verified since the currently available physically transient memristors are still in micron scale. Therefore, wafer-scale fabrication technology for nanodevices and integrated arrays is required. For bio-integrated systems, it is desirable that the operation voltage of transient memristor neuromorphic devices is compatible with the action potential of bio-systems to meet the requirements of brain—machine communication [85]. But the operation voltages of transient memristors far exceed the low bio-voltage. In addition, how to connect artificial devices with living biological systems to realize intelligence brain—machine interfaces needs to be explored. For general applications, triggering methods for transient electronic devices disappearing are very important. Careful and accurate designing of transient neuromorphic systems is needed to control and program their degradation rates and disappearance times.

#### 5.3. Advances in science and technology to meet challenges

The development of physically transient neuromorphic systems from concept to application will meet serious challenges. With the advances in science and technology through efforts from multiple areas of the research community, overcoming challenges from materials to devices to integrated systems is desirable. Because of the contradiction between stability and degradability, materials with different chemical properties are expected to form unique multilayer stacked structures to maintain stable electrical performance in air and rapid degradation in biofluids and/or water. In addition, designing of special chemical bonds in the material system is also possible to achieve such demands. Protection or encapsulation layers are an effective choice for transient memristors to ensure stability of their electrical performances before they disappear. Based on developed materials, the endurance and uniformity of the devices can be enhanced by referring to the proposed methods for conventional memristors, such as controlling the size and shape of CFs.

For large-scale integrated arrays, selecting of wafer-scale and nano-fabrication technology-compatible materials is the most effective option for material and device-level feasibility. Furthermore, a technology called transfer printing, which can transfer devices and circuits on top of wafers to various hetero-substrates such as degradable substrates, is an ideal fabrication technology for integrated transient neuromorphic systems [86]. With advances in materials and transfer printing, it is no doubt that the size of devices can scale down. Fully implemented transient memristor arrays also depend on the progress of the whole transient electronic area. Transient transistors that can fit with transient memristors would greatly boost the realization of physically transient neuromorphic systems. For bio-integrated systems, deep understanding of ionic transport properties both from materials and biological view is helpful in controlling ionic transport to design bio-voltage transient memristors for brain—machine communication. The degradation of transient devices that results in their disappearance can be controlled by applying external forces, such as thermal force, light, and fluids, to these devices [87]. With combined effects from the areas of materials, physics, engineering, etc, and with advances both in software and hardware, physically transient memristors will show promising applications (figure 5).

#### 5.4. Concluding remarks

Physically transient electronic devices that can disappear on demand would lead to transformative new applications. Physically transient memristors, which integrate the advantages of transient electronics and neuromorphic computing, may yield various innovative applications, such as biological interactive intelligence and security computing. The development of transient memristors is just beginning, and great advantages for application have not yet been demonstrated. The main challenges range from materials design to fabrication technology to system application, including the contradiction between stability and degradability, wafer-scale and nano-fabrication technology, and degradation trigger methods. To overcome these challenges needs effort and cooperation from different disciplines. We believe that breakthroughs in chemistry and materials science will resolve the contradictions between stability and degradability for transient memristors. Research progress of materials and electrical engineering will achieve larger-scale integration technology of physically transient neuromorphic devices. Joint research of materials, devices, integration technology, and even biology both from theoretical and experimental views will pave the way for biological integrated intelligence.

#### Acknowledgements

This work was supported by the National Key Research and Development Program under Grant 2018YFB2202900, National Natural Science Foundation of China (61574107), Opening Project of Key Laboratory of Microelectronic Devices and Integrated Technology, and Institute of Microelectronics of the Chinese Academy of Sciences.

# 6. Recent advances in transistor-based organic synapses in China: from device to system

Junyao Zhang and Jia Huang Tongji University, People's Republic of China

E-mail: 1910586@tongji.edu.cn and huangjia@tongji.edu.cn

#### 6.1. Status

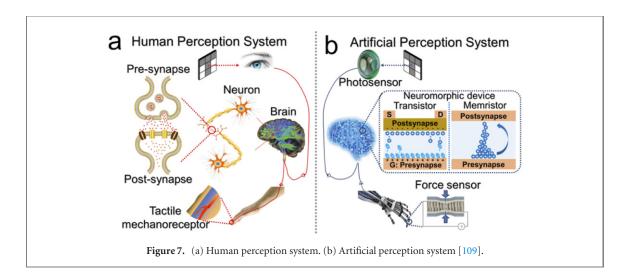

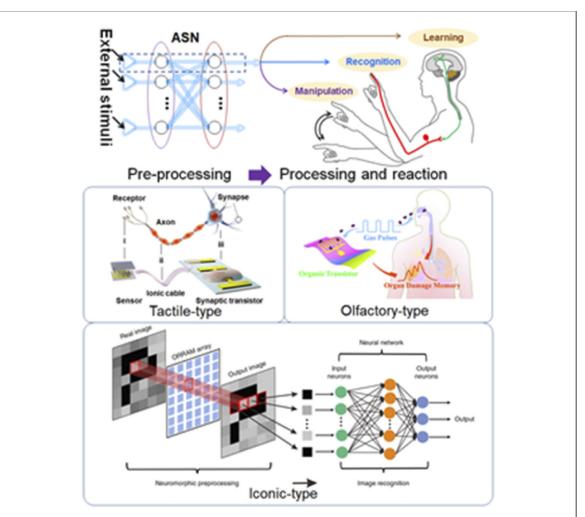

Driven by the development of next-generation artificial intelligent systems, the requirement for neuromorphic electronics that can emulate fundamental functions of the human nervous system is significantly increasing [88]. The human nervous system, which consists of  $\sim 10^{11}$  neurons and  $\sim 10^{15}$  synapses, can be divided into the peripheral nervous system (PNS) and the central nervous system (CNS) [89]. The CNS is capable of calculating and storing massive information simultaneously obtained from the PNS, which has merits of lower energy consumption and faster information processing compared with von Neumann computers. Synaptic plasticity and its event-driven update functions through repetitive spike-form stimulations can be considered as primary elements of energy-efficient computing. Thus, the development of artificial intelligent computing systems at a hardware level demands the construction of neuromorphic electronics with the ability to simulate key factors for processing and memory performance of the CNS. Furthermore, the PNS is composed of sensory and motor nerves and organs. Human beings detect numerous stimuli from the complicated environment and make proper instructions through the cooperation of the CNS and PNS. External stimuli are perceived through the sensory part of the PNS and processed through the CNS, and then corresponding behavioral instructions are given by the motion part of the PNS. Hence, artificial intelligent systems can be developed with the cooperation of neuromorphic electronics, which are capable of accurate perception, efficient data processing, and motor coordination.

Organic synapses are representative components of neuromorphic electronics, which enable to mimic synaptic plasticity and correlative functions [90]. Organic materials have many merits of easy processability for solution-processing techniques, low cost, and simple regulation by molecular properties [91]. Moreover, compared with inorganic materials, organic materials with outstanding ductility and biocompatible mechanical performance are desired for flexible devices, which have promising application prospects in future wearable and bioinspired electronics and robotics. Organic synapses have attracted wide interests of researchers all over the world, and then different kinds of device configurations are proposed. Compared with two-terminal synaptic devices, three-terminal synaptic transistors can execute signal transmission and self-learning concurrently [91]. Also, they can have multiple gates to receive signals from diverse sources at the same time, so dendrite integration and spatiotemporal effect can be realized. Through suitable structure design and material selection, synaptic transistors can transform external stimuli into electrical signals, which makes them possible to realize neuromorphic electronics that directly respond to the surrounding environment. Chinese researchers have made many remarkable contributions in the field of transistor-based organic synapses.

#### 6.2. Current and future challenges

One of the biggest challenges in transistor-based organic synapses is to imitate various biological synaptic characteristics. According to Hebb's theory, short-term plasticity, long-term plasticity, STDP, and spike-rating-dependent plasticity are basic forms of synaptic plasticity [92]. Consequently, it is believed that synaptic devices should simulate these neuroplastic behaviors. Also, it is expected that full synaptic characteristics can be emulated in the next 10 years. Next, energy efficiency is regarded to be a significant factor in constructing an artificial intelligent system based on synaptic devices. A biological synapse consumes  $\sim 10 \, \mathrm{fJ}$  per synaptic event; it is essential to find effective ways to decrease the power consumption [91]. Most of the present transistor-based organic synapses have a large gap with the biological counterparts in terms of energy consumption and device size [88]. Besides, since flexibility and stretchability are the extremely important advantages of organic transistors, it is rational to apply transistor-based organic synapses in flexible, conformable, and stretchable neuromorphic electronics [89].

With the successive advancement of transistor-based organic synapses, hardware achievements of artificial intelligent systems have been in the spotlight. The major research objective of neuromorphic electronics is to simulate the neuromorphic computing functions of the human brain in hardware. Besides basic synaptic functions, remarkable progressive neuromorphic computing functions should also be emulated. Transistor-based organic synapses must be integrated in the form of arrays to implement system-level neuromorphic computing. Most studies have still utilized algorithms to establish ANNs for the simulation of system-level neuromorphic computing based on the characteristics of one or several devices. The hardware implementation of ANNs based on organic synaptic transistors requires further efforts, which can be one goal for the next

**IOP** Publishing **2** (2022) 042501 Roadmap

**Figure 5.** Challenges and possible solutions for physically transient memristors. The hierarchical architecture from materials to devices to integrated systems needs to be optimized in collaboration with each other.

**Table 2.** Summary of transistor-based organic synapses in China.

| Type | Materials                                                                                                                            |

|------|--------------------------------------------------------------------------------------------------------------------------------------|

|      | Floating gate: C <sub>60</sub> , perovskites, reduced graphene oxide, metal-organic frameworks, topological insulators, carbon dots, |

|      | 2D imine polymers, black phosphorus-ZnO hybrid nanoparticles, and upconverting nanoparticles                                         |

| FGT  | Tunneling layer: PMMA, PS, and silk                                                                                                  |

|      | Channel: pentacene, IDTBT, and PDPP4T                                                                                                |

|      | Active additives: perovskites, MoS <sub>2</sub> , porphyrin, PLA, and chlorophyll                                                    |

|      | Dielectric: PAN and SiO <sub>2</sub>                                                                                                 |

| CTT  | Channel: carbon nanotubes, C8-BTBT, DNTT, PDPP4T, DPPDTT, TIPS-pentacene, PQT-12, and PTCDA                                          |

|      | Electrolyte insulator: ionic liquid, ion gels, and solid-state electrolyte                                                           |

| EGT  | Channel: POT-12, C8-BTBT, P3HT, IDT-BT, PEDOT: PSS, DNTT, and rubrene                                                                |

|      | Ferroelectric insulator: P(VDF-TrFE)                                                                                                 |

| FeGT | Channel: graphene and PIID-BT                                                                                                        |

10 years. The hardware implementation of ANNs may also encounter next-level issues, such as uniformity, endurance, reliability, interconnection, and complicated processing problems.

In addition to neuromorphic computing applications, transistor-based organic synapses should also be explored to build artificial perception and motor systems. Through proper suitable structure design, material selection, and device integration, artificial perception systems should be able to convert external stimuli (light, pressure, smell, sound, etc) from the external environment into electrical signals. Then, the corresponding behavioral instructions can be manipulated through artificial motor systems. These bionic processes are similar to sensing and motoring functions of biological sensory systems. It is of great significance to develop a comprehensive artificial intelligent system that can realize multiple perception and motor functions in the next 5 years.

#### 6.3. Advances in science and technology to meet challenges

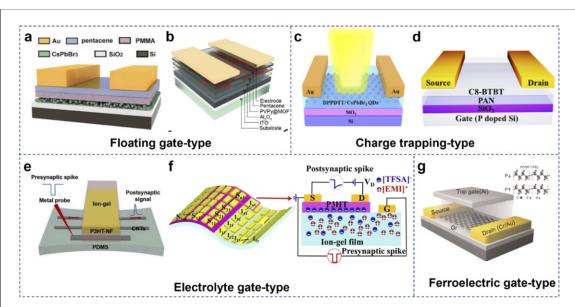

Through desirable device configuration and material selection, different kinds of transistor-based organic synapses for the hardware implementation of next-generation artificial intelligent systems have been widely studied. So far, four kinds of transistor-based organic synapses have been presented, including floating gate transistor (FGT), charge trapping transistor (CTT), electrolyte gate transistor (EGT), and ferroelectric gate transistor (FeGT) (table 2).

IOP Publishing

2 (2022) 042501

Roadmap

**Figure 6.** (a) Device structure of a photonic FGT based on CsPbBr<sub>3</sub> QDs [93]. Copyright 2018, Wiley-VCH. (b) Schematic diagram of a 2D MOF-based FGT [94]. Copyright 2019, Wiley-VCH. (c) Schematic diagram of a CTT based on CsPbBr<sub>3</sub> QDs [95]. Copyright 2020, American Chemical Society. (d) Schematic diagram of a PAN-based CTT [96]. Copyright 2018, American Chemical Society. (e) Device structure of a stretchable EGT based on wavy networks P3HT nanofibers [98]. Copyright 2020, Elsevier B.V. (f) Schematic diagram of multiterminal EGTs with a highly interconnected neuromorphic architecture of multi-inputs and multi-outputs [99]. Copyright 2018, American Chemical Society. (g) Device structure of a FeGT [101]. Copyright 2019, Springer Nature.

FGTs possess a large on/off ratio and a controllable channel conductance. Thus, they are suitable to achieve long-term synaptic potentiation and depression functions. Both 0D materials [93] and 2D materials [94] (figures 6(a) and (b)) have been extensively explored for the construction of FGTs. For CTTs, charge carriers can be trapped at active additives and active additives/organic semiconductor (OSC) interfaces [95] (figure 6(c)) or dielectric/OSC interfaces [96] (figure 6(d)). Trapped charges offer an extra electric field, leading to a regulatable channel conductance, which is a platform for emulating synaptic characteristics. EGTs are capable of using ions in electrolyte dielectric to adjust the channel conductance. Conformal EGTs with the combination of flexible material components have been reported, which presented remarkable conformability on 3D curved surfaces [97]. Besides, to satisfy compatibility with dynamic surfaces for practical applications, stretchable EGTs were explored [98] (figure 6(e)). Biologically, a neuron is capable of receiving multiple input signals, and each received signal can be transmitted to numerous neurons. Similarly, multiterminal EGTs with a highly interconnected neuromorphic architecture of multi-inputs and multi-outputs were demonstrated [99] (figure 6(f)). More importantly, EGTs with low operating voltage are appropriate for low-energy-consumption synaptic devices. A low power consumption of 0.29 fJ per synaptic event was implemented in organic single-crystalline nanoribbon-based EGTs [100]. Ferroelectric insulator with spontaneous polarization states is the critical component in ferroelectric gate transistors. The channel conductance of FeGTs can be gradually controlled through the modulation of polarization states in the ferroelectric insulator. FeGTs utilizing P(VDF-TrFE) ferroelectric polymer as the gate dielectric were demonstrated [101] (figure 6(g)). Through the gate adjusting, both hole-dominated and electron-dominated transport could be realized, leading to tunable bipolar characteristics.

For neuromorphic computing systems, significant progressive functions, including logic operation [95], filtering [102], and association learning [98], have been successfully achieved. In addition, different kinds of artificial perception systems have been explored, such as visual- [103], tactile- [104], olfactory- [105], and auditory-perception systems [106]. Artificial motor systems have also been built with the combination of an organic synaptic transistor and an artificial motor element [107]. These bionic processes are similar to sensing and motoring functions of biological nervous systems.

# 6.4. Concluding remarks

Many efforts have been made by Chinese researchers in both material and structure to design novel transistor-based organic synapses that can emulate biological synapses with similar functions and energy consumption level. Although neuromorphic systems based on organic synaptic transistors have been implemented in a wide range of applications, the development of artificial intelligent systems is still in an early stage, and various challenging issues remain to be addressed for practical applications. For example, only a small number of synaptic functions have been emulated. Full biological synaptic characteristics and complete human perception systems should be imitated. Up to now, artificial perception systems have the capability of sensing only one

type of sensing signals, which limit the efficient resolution for the coupling issue of sensing information in the future. By integrating diversified fields, such as materials science, microelectronics, medicine, and computer science, we speculate that the large-scale deployment of artificial intelligent systems will no longer be a dream.

# Acknowledgements

This work was supported by the National Natural Science Foundation of China (62074111), Science & Technology Foundation of Shanghai (19JC1412402 and 20JC1415600), Shanghai Municipal Science and Technology Major Project (2021SHZDZX0100), and Shanghai Municipal Commission of Science and Technology Project (19511132101).

# 7. Brief discussion of oxide neuromorphic transistors in China

Zheng Yu Ren<sup>1,2,3</sup>, Li Qiang Zhu<sup>1,2</sup> and Qing Wan<sup>4</sup>

- <sup>1</sup> Ningbo University, People's Republic of China

- <sup>2</sup> Chinese Academy of Sciences, People's Republic of China

- <sup>3</sup> ShanghaiTech University, People's Republic of China

- <sup>4</sup> Nanjing University, People's Republic of China

#### 7.1. Status

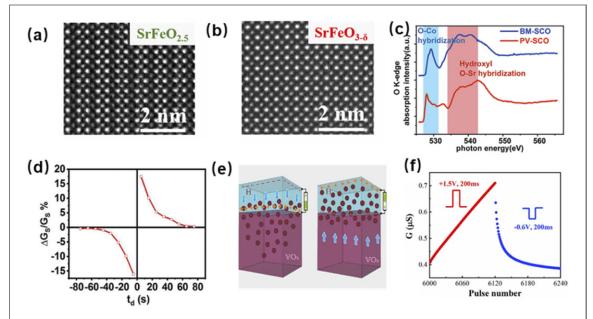

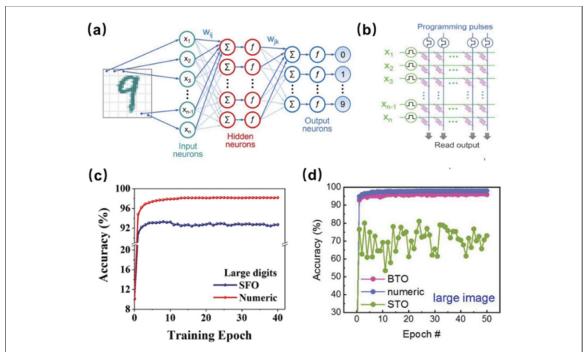

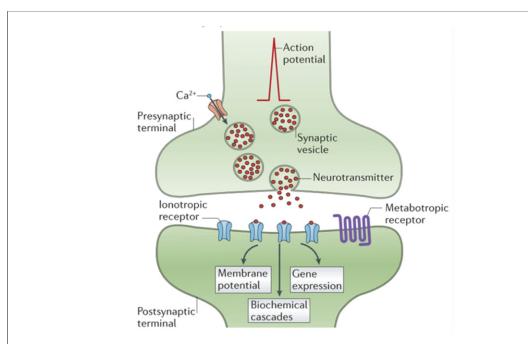

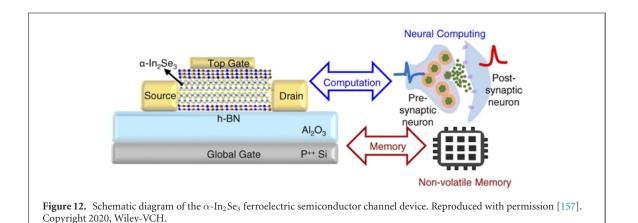

Von Neumann architecture is highly efficient in dealing with structural data. However, it is less energy efficient in dealing with intelligent tasks. Especially with the developments of IoT technology, it is necessary to process massive amounts of data in an energy-efficient way. Thus, new computation architectures are highly desirable in dealing with such tasks. In 1950s, John McCarthy *et al* have proposed AI, aiming to mimic human brain [108]. Especially after the success of the AI robot 'AlphaGo', studies on AI have aroused worldwide attention. With deep learning technology, AI has entered into a new era in the fields of speech, image processing, and natural language. Conventionally, AI is built based on von Neumann architecture and complex computer programming codes. However, high energy consumption is always needed because of the limited parallel computation that originated from physical separation of computation modules and memory units in von Neumann architecture (i.e. the von Neumann bottleneck).